# 一、Quartus 及驱动安装

# 1.1 Quartus 安装

根据百度网盘中的安装包及教程进行软件安装

# 1.2 驱动安装

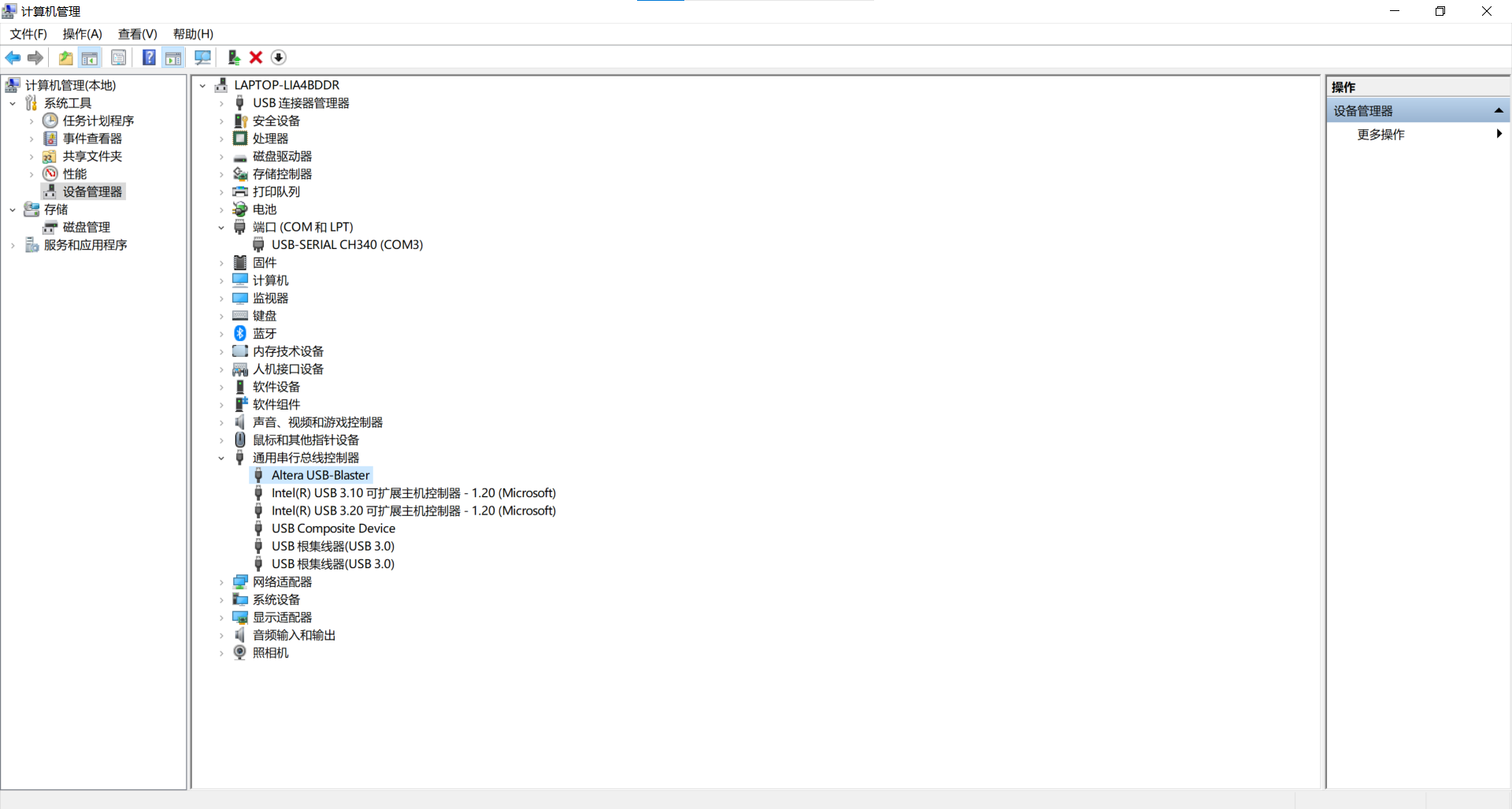

FPGA 与计算机共有两条数据线进行连接,一条用于供电及通讯,另一条用于程序的烧录。将 FPGA 开发板正确连接至电脑后,可在设备管理器中看到如 USB-SERIAL CH340 及 Altera USB-Blaster 则证明 FPGA 与计算机连接成功。(⚠️若小图标处有感叹号,则证明缺少驱动,可根据安装教程进行驱动安装,本次安装的电脑为重装后的电脑,没有安装任何驱动即可正确识别)

# 二、Modelsim 安装

安装 Modelsim ,安装包及教程见百度网盘

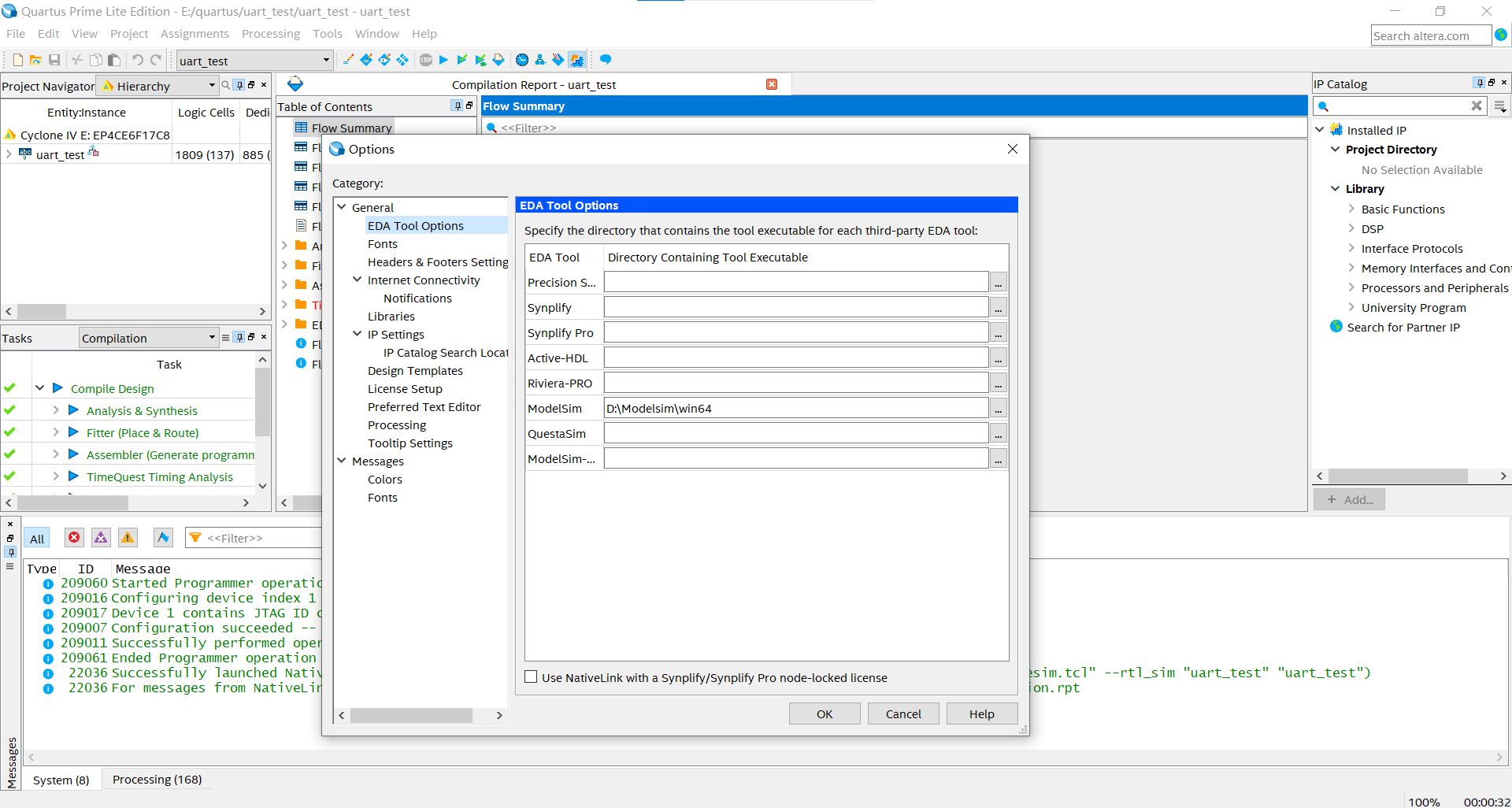

安装完成 Modelsim 后,在 Quartus 中依次点击 Tools→Options→General→EDA Tool Options 选择 Modelsim 的安装路径里面的 win64

# 三、程序编译

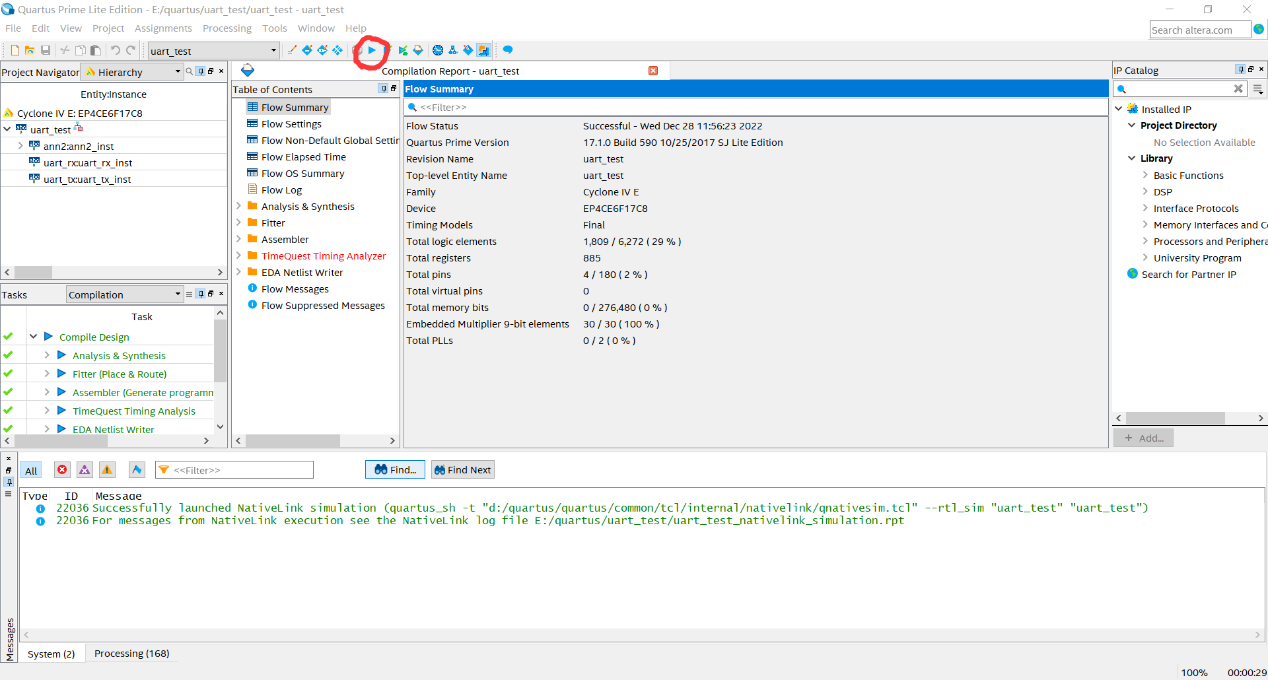

进入 Quartus 软件,点击 start compilation 进行程序编译

# 四、仿真

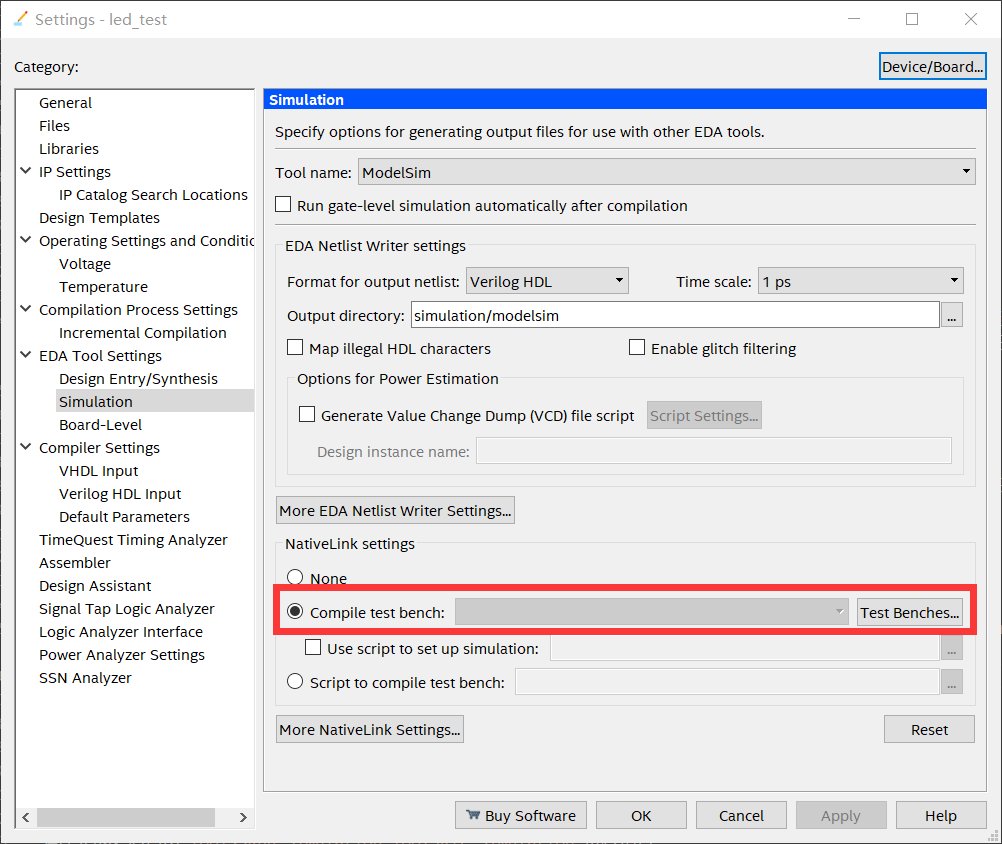

(以下为测试脚本设置过程,项目已经设置好,作为普及)依次点击 Assignments→Settings 。打开后点击 EDA Tool Settings→Simulation ,之后在 NativeLink settings 中选择 Compile test bench

选择测试脚本(点击 Test Benches…→new )

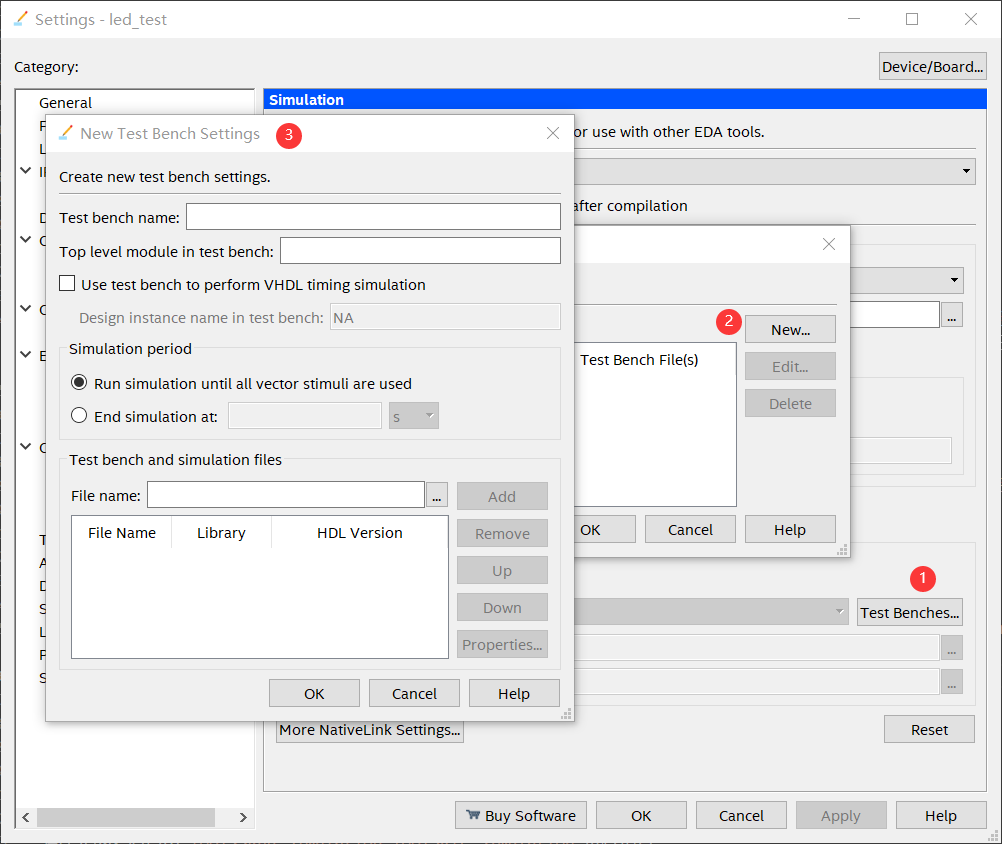

图中从上往下:

StandardTR是系统建立testbench文件.vt的名字。StandardTR_vlg_tst是.vt里面的module的名字。- 点击

Fill name右边的…选择.vt文件,点击add。

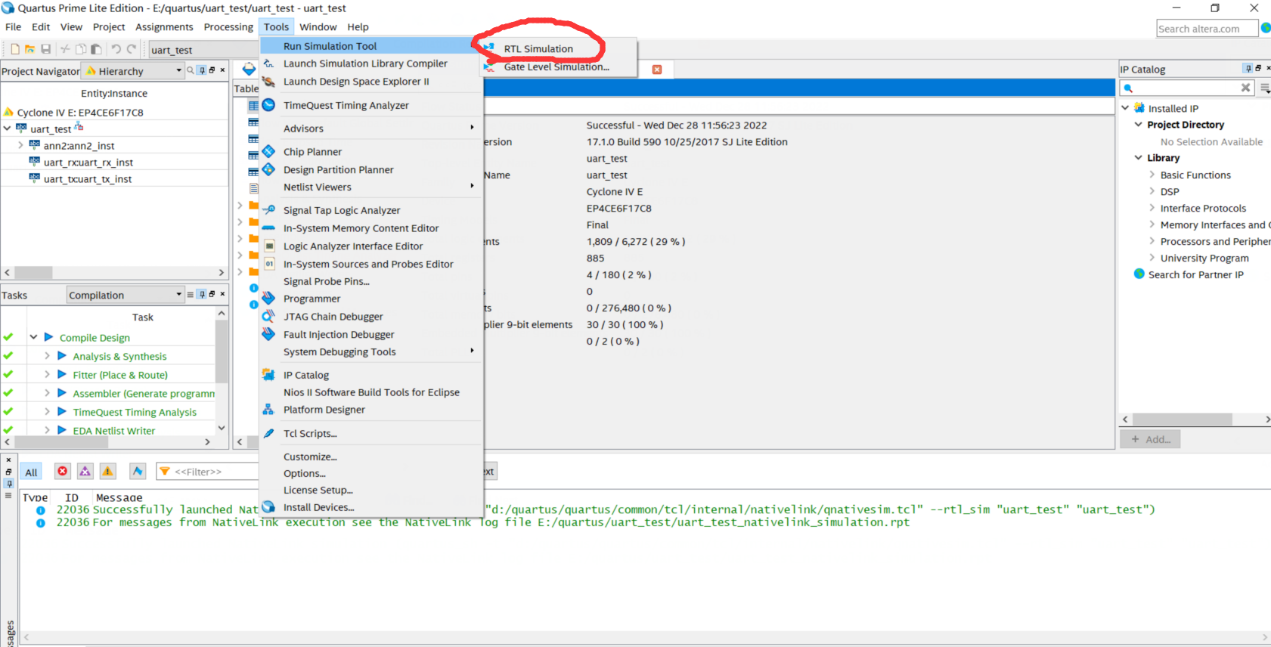

(以下过程为正式仿真过程,需要运行)在完成以上步骤及编译完成之后点击Tools→Run Simulation Tool→RTL Simulation进行仿真

![]()

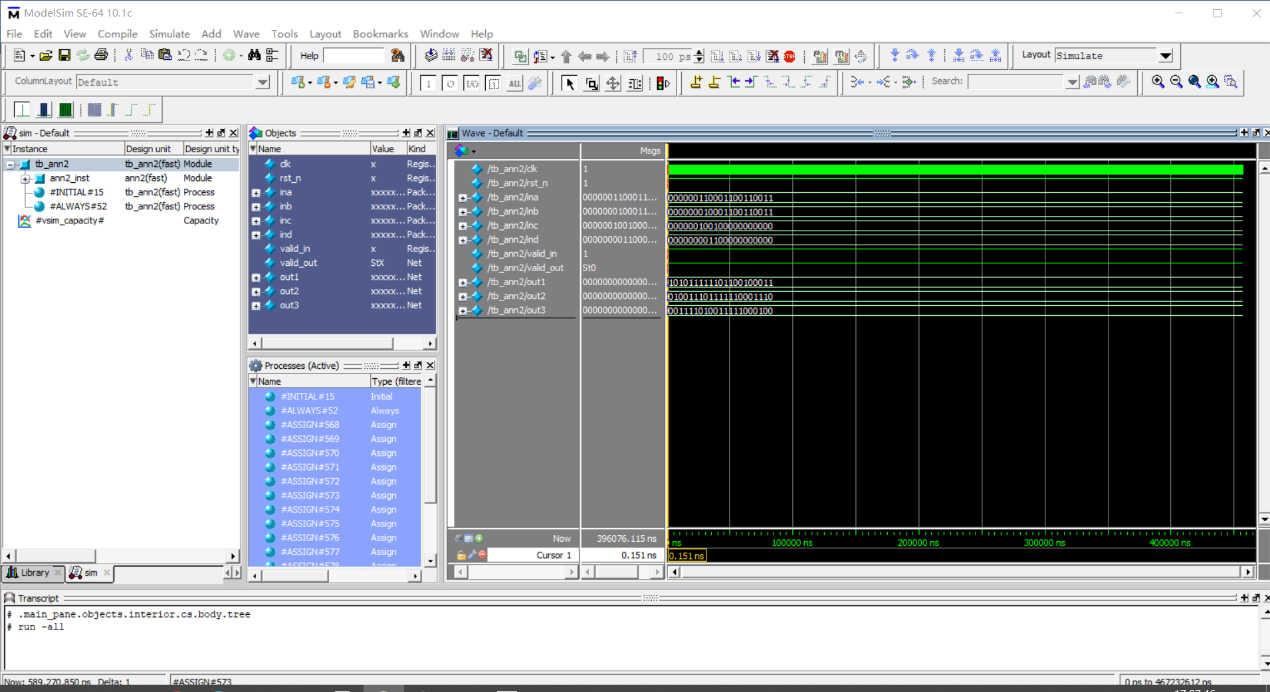

仿真完成后可显示如下界面(点击Zoom full可显示波形)

![]()

# 五、程序下载至 FPGA

如下图所示将 FPGA 与电脑连接连接

其中 USB Blaster 为编程时,电脑给开发板传输程序文件的数据线,在传输完程序之后即可移除(不拔出来也没事儿)。

USB to TTL 为开发板提供电源功能、并在串口调试阶段作为电脑与开发板进行数据交换的线。

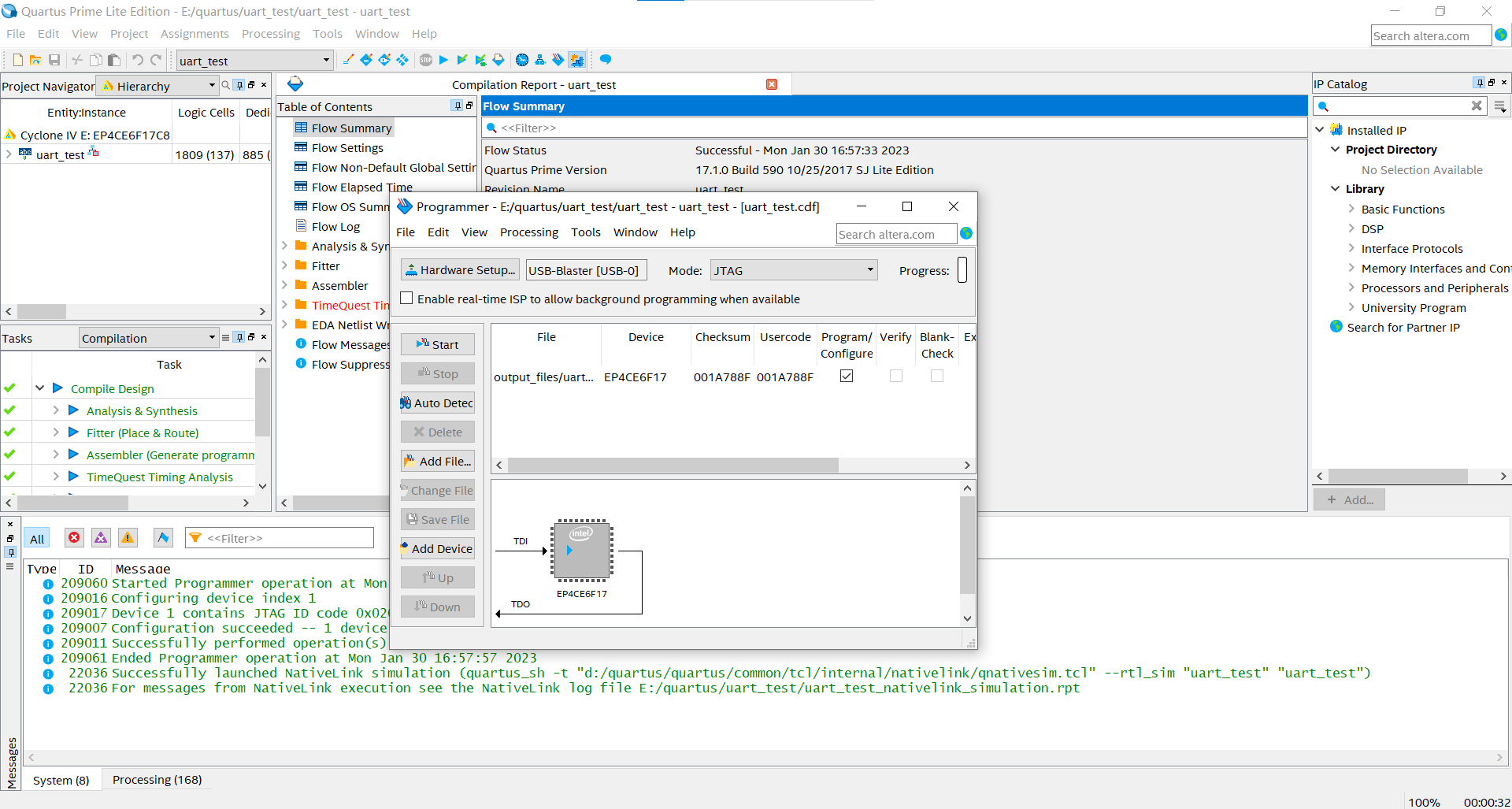

在 Quartus 中依次点击 Tools→Programmer 打开如下界面

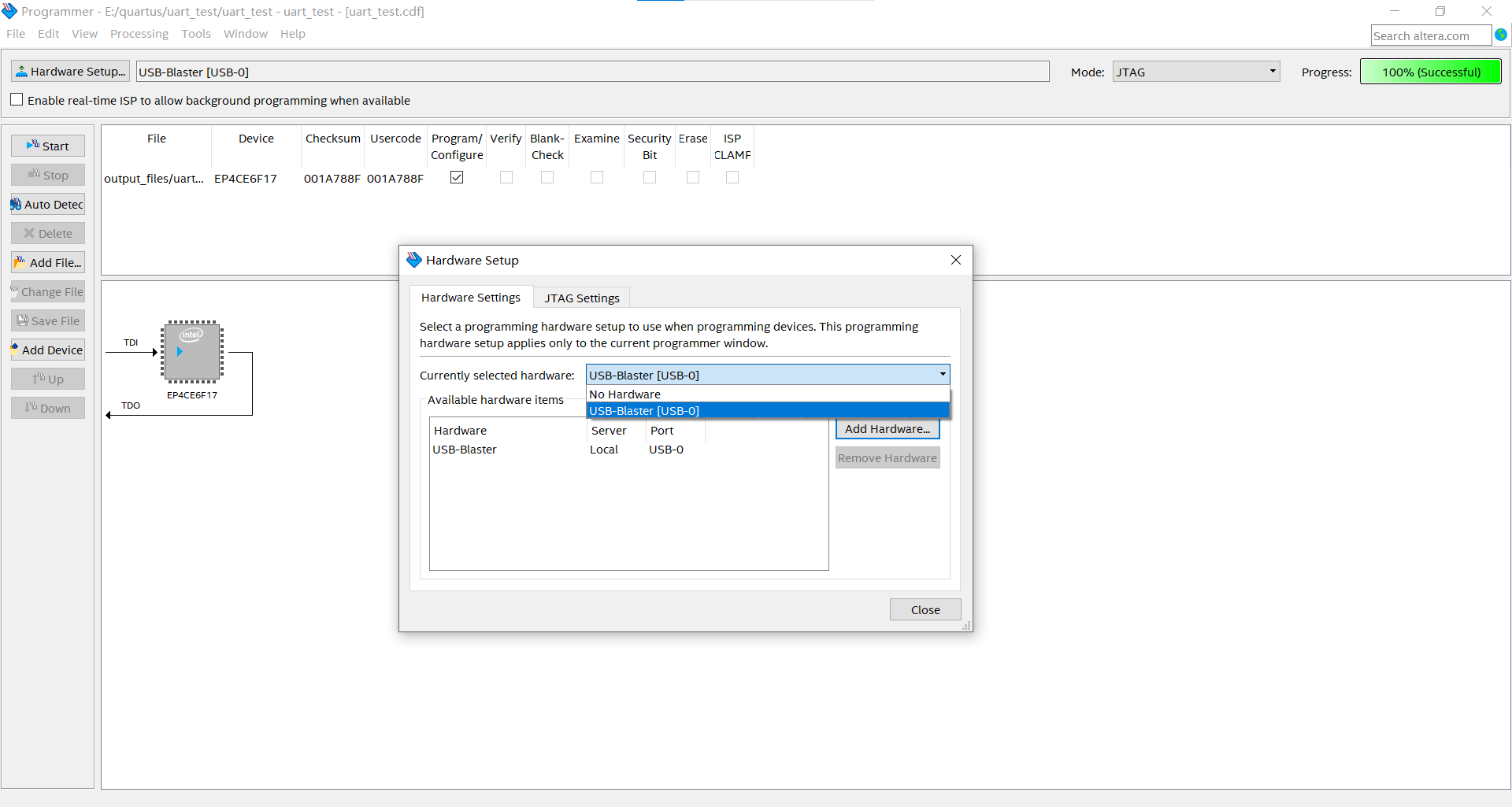

点击 Start 即可开始程序下载,若未识别到硬件,可点击 Hardware Setup 进行设置,如下图所示

# 六、串口展示

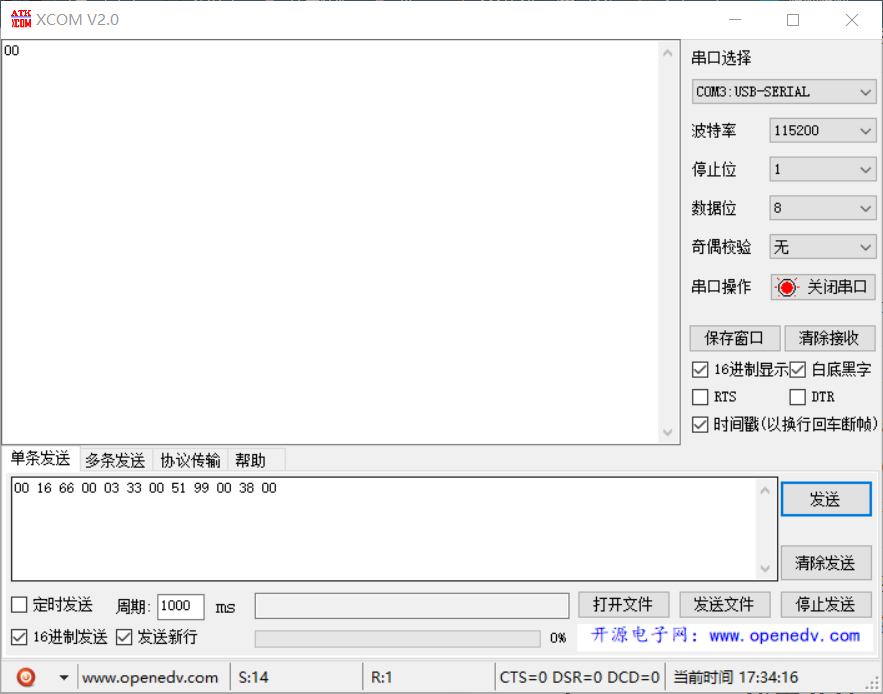

打开 XCOM (串口调试助手,就是电脑和开发板进行数据交换的软件),波特率设置为 115200 、选择 16 进制显示、 16 进制发送,如下图所示。

在设置完成后点击打开串口,在下方数据发送区输入数据 (只能依次输入,不能直接复制),点击发送后即可在数据接受区得到 FPGA 运行后的结果,每次运行后都需要按下 FPGA 上的 key1 键进行复位。

# 输入数据的获取

点击此处可获得鸢尾花原始数据集,如下图所示

每一行为一条数据,每一列依次表示花萼长、花萼宽、花瓣长、花瓣宽以及花的类型

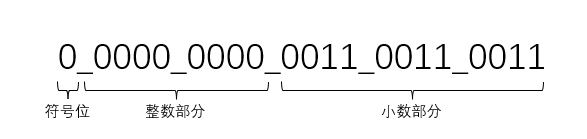

将每条数据的十进制数据转换为如下格式的二进制数据

以第一行数据为例,四个数据转换分别为:

5.1 = 0 0000 0101 0001 1001 1001

3.5 = 0 0000 0011 1000 0000 0000

1.4 = 0 0000 0001 0110 0110 0110

0.2 = 0 0000 0000 0011 0011 0011

再将以上数据转换为 16 进制格式,如下所示

0 0000 0101 0001 1001 1001 = 00 51 99

0 0000 0011 1000 0000 0000 = 00 38 00

0 0000 0001 0110 0110 0110 = 00 16 66

0 0000 0000 0011 0011 0011 = 00 03 33

最后依次拼接即可获得输入数据 (需要调整一下顺序,我们的输入顺序是花瓣长、花瓣宽、花萼长、花萼宽,网页数据顺序为花萼长、花萼宽、花瓣长、花瓣宽) 00 16 66 00 03 33 00 51 99 00 38 00

# 七、Quartus 使用总结

Quartus 的使用步骤可以大致总结为:

- 程序编译(根据想要实现的逻辑进行程序编写)

- 程序仿真(在完成程序编译之后,并不确定程序的正确性,可以先在仿真系统中进行仿真运行,即在电脑上先预览程序的正确性,此步骤为可选步骤)

- 程序下载至 FPGA(此过程即为将程序下载至 FPGA,从而使 FPGA 可以根据程序实现一定的功能,并使用串口将 FPGA 的运行结果可视化展现)